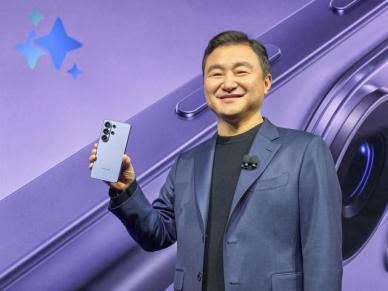

송재혁 삼성전자 반도체(DS) 부문 최고기술책임자(CTO)는 22일 서울 삼성동 코엑스에서 열린 제27회 반도체대전(SEDEX 2025)에서 이같이 말했다. 이날 '시너지를 통한 혁신'을 주제로 기조 강연을 진행하며 기술 간 협업과 통합이 반도체 발전의 핵심 동력임을 강조했다.

송 CTO는 특히 "실리콘이 할 수 있는 것도 벽을 만나기 시작했다"며 "실리콘 원자가 줄어들면 기존의 설계 기반 시뮬레이션 툴이 상당히 영향을 받을 것"이라고 설명했다. 이를 극복하기 위한 방법으로 '경계를 넘는 협업'을 제시했다.

그는 "실리콘의 기술 한계가 온다는 전제로 고객이 원하는 파워, 성능, 면적당 효율을 공급하기 위한 다양한 패키지 기술들도 개발돼야 한다"며 "실제 업계는 칩이 평평하다가 세우고, 이제는 붙이고 쌓는 과정으로 발전하고 있다"고 말했다.

이어 "D램에서도 곧 버티컬 채널 트랜지스터(VCT) 기술이 등장할 것"이라며 "D램은 V낸드가 갔던 길처럼 가야 채널을 세웠을 때 대비 혁신적으로 칩 크기를 줄일 수 있을 것"이라고 설명했다.

이제는 '붙이는' 단계다. 송 CTO는 "이제는 셀과 셀을 붙이는 것은 이미 상용화된 기술이고 로직은 백사이드에서 파워를 공급해서 효과적으로 배터리를 쓰려고 노력하다 보니 역시 붙여야 되는 경우들이 생기고 있다"고 말했다.

마지막 단계는 '쌓는' 것이다. 그는 "로직도 이제는 트랜지스터로 쌓여야 하는 방향으로 잡고 가고 있다"며 "칩렛이 끝판왕이 될 것"이라고 전망했다. 그는 "칩렛으로 연결된다는 것은 실리콘이 할 수 있는 것도 벽을 만난다는 의미"라고 덧붙였다.

삼성전자는 이러한 기술적 한계를 극복하기 위해 내부 조직 간 융합을 강화하고 있다.

송 CTO는 "삼성은 전 세계에서 D램, 낸드, 로직, CIS, 패키지까지 전 라인업을 갖춘 유일한 기업"이라며 "예전에는 너무 많은 부담이 아닌가 생각했지만 지금은 오히려 더 좋은 시너지를 낼 수 있을 것 같다"고 말했다.

실제로 삼성 내부에서는 기술 융합이 활발히 진행 중이다. 송 CTO는 "본딩, 하이 퍼포먼스 트랜지스터, 파인 패턴 같은 카테고리로 묶으면 D램, 플래시, 로직, 어드밴스드 패키지가 동일한 성격의 기술들로 조합돼 각 팀이 협업하고 있다"고 설명했다.

특히 AI 시대를 맞아 변화가 가속화되고 있다. 그는 "플래시까지도 상당한 스피드를 요구하고 있다"며 "로직, D램, 플래시가 함께 일하면서 특정 기술이 각 분야에 적용되는 데 수정이 필요하지만 전혀 다른 과목이 아닌 것 같다"고 말했다.

송 CTO는 반도체 기술이 예상 밖의 분야와 연결되고 있다고 밝혔다. 그는 "웨이퍼 레벨의 휨, 패키지 휨 등 모든 부분이 응력(stress) 방정식으로 설명된다"며 "요즘 그런 생각이 든다. 삼성반도체가 지진 전문가를 좀 채용해야 하지 않을까"라고 말했다.

이어 "예전에는 10개 부서가 일을 했으면 되는데 이제는 20개, 30개 부서가 같이 일을 해야만 발생될 수 있는 기술적 난이도가 되고 있다"며 마지막으로 "그런 의미에서 소자, 공정, 소재 등 다양한 분야의 업체와 학계, 산업계와 기술 개발을 하고 싶다"고 밝혔다.

Copyright © 이코노믹데일리, 무단전재·재배포 금지